How can we model a circuit’s power without knowing its structure?

Energy is crucial in integrated circuits and is determined by their implementation. Missing information in early design stages or for external designs limits the achievable accuracy of power models. We studied efficient data generation and precise machine learning methods to overcome this gap, and we identified the low variance of graph neural networks and the high accuracy of linear models for circuits. The results show potential for early power estimation.

Focus Group: Machine Learning for Energy Analysis

Dr. Sani Nassif (Radyalis LLC), Alumnus Rudolf Diesel Industry Fellow | Philipp Fengler (TUM), Doctoral Candidate | Host: Prof. Ulf Schlichtmann (TUM)

Integrated circuits (ICs) are an integral part of our lives today. Used as microcontrollers in small household devices, as well as for high-performance computing clusters, the design of the circuits faces challenges including minimization of costs as well as safety and security requirements. Estimating the power dissipation of the final design is required to control many of these challenges. Power dissipation not only correlates directly with the operating costs of the IC, but also influences the optimality of the design due to safety margins. These margins are necessary to prevent damage and to maintain the correct functionality of the circuit. Power estimation is most accurate with resource-expensive methods in the late design stages. But modifications of the circuit at this stage are much more costly and negatively impact time to market. Therefore, precise power estimation at early design stages is of great importance.

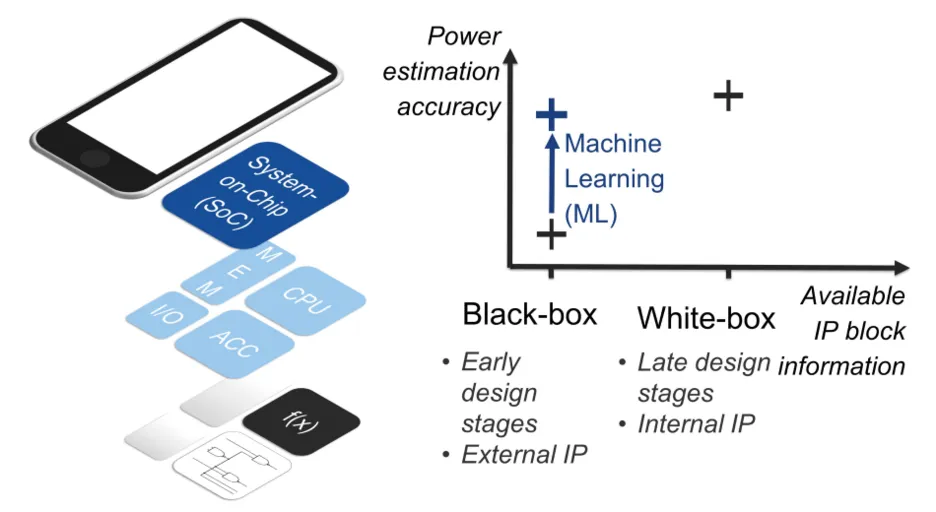

Figure 1

Hierarchical IC design and limitations for power estimation

Due to the miniaturization of the fundamental element of digital ICs, the transistor, it is common to have circuits with billions of devices. Handling such complexity requires a high degree of automation and the reuse of existing components, and it mandates the use of a hierarchical approach. Fig. 1 shows an example of such a hierarchy for a smartphone on the left-hand side. Various functional blocks of the phone are packed into one integrated circuit, the system-on-chip, but need not be redesigned for every phone model and are often reused from a library of intellectual property (IP) blocks or sourced from external vendors. For example, the smartphone’s central processing unit (CPU) may be obtained from a specialist for this circuit type, while a custom circuit to accelerate machine learning (ML) applications is designed in-house. Therefore, depending on the design stage of the circuit (block) and the information provided by external vendors, an IP block's actual structure and implementation may not be available and can be described as a black box.

Power dissipation of ICs has different sources. One dominant kind is dynamic power dissipation. It happens while charging and discharging capacitances within the circuit. Therefore, it is closely related to the change of signal values within the circuit, described by switching activity. While the functionality of the circuit (e.g., logic functions) already gives a basis for estimating the switching activity of an IC design, it may differ significantly from the final switching activity of a circuit. Due to the circuit’s structure, signals can have different latencies, leading to switching events not captured by the functionality alone. Obtaining the switching activity of an IP block for its final stage is required to enable highly accurate dynamic power estimates.

Fig. 1 on the right-hand side qualitatively shows the limitations of power estimation accuracy on black-box designs. The missing information on the circuit structure in early design stages or for IP blocks from external providers also limits the achievable accuracy. Our Focus Group investigated the opportunities that data-driven approaches such as ML provide to overcome the lack of information here. Recent research has also focused on power dissipation becoming more influential not only for small battery-based devices, but also in large server clusters. In addition, mamachine learning, such as graph neural networks (GNN), shows promising results. For example, GRANNITE [1] shows that a data-driven switching activity model can be applied to various circuit types. However, it is based on detailed information about the structure of the circuit and hence is not applicable to our use case.

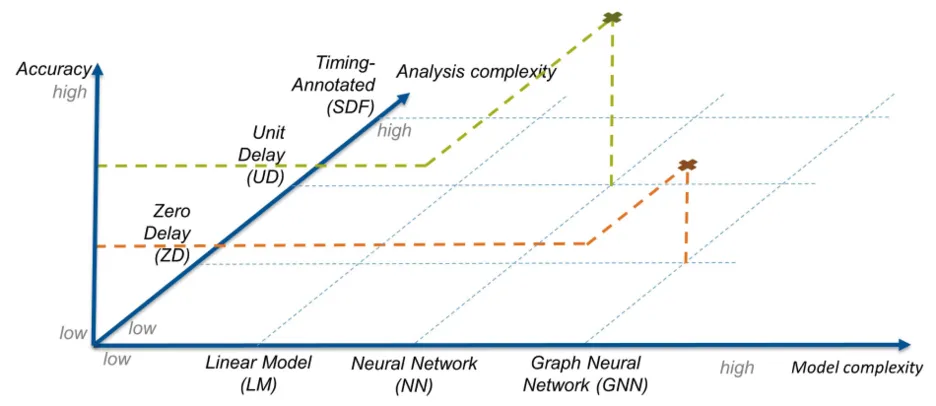

Figure 2

Data-driven power modeling for black-box circuits

As diverse as the applications of ICs are today, the approaches to performing power estimation are just as diverse. For ML-based methods, existing circuit designs must be characterized by their power dissipation behavior. Measurements, simulation, and statistical methods have been used here [2]. At the beginning of the Fellowship program of our Focus Group, we identified suitable available circuit designs and power estimation frameworks to generate data. As researchers have investigated the power consumption of ICs for decades, we first focused on using available domain knowledge on power dissipation to develop suitable modeling methods. This fusion is often referred to as physics-based or -informed ML [3]. We investigated the design of neural network-based modeling using the theoretic knowledge of power dissipation of ICs. However, due to limited knowledge of the circuit design in our black-box scenario, such a physics-based, i.e., in our case, circuit structure-based, approach is barely applicable.

Therefore, we moved our focus to identifying the most suitable data-driven approach for early-stage and black-box circuit designs. Modern integrated circuits can contain billions of transistors. Therefore, the modeling approach has to be suitable for dealing with very many circuit signals. This results in a decision for the modeling method and how to obtain the data to fit the model. Fig. 2 shows this decision space qualitatively. Circuit analysis by simulation can be done using different timing models (where “zero delay” means, for example, that circuit propagation delays are not considered). On the other hand, different modeling approaches will result in different obtainable accuracies. If both dimensions are combined, the actual accuracy of a modeling framework can be assessed. Within this project, we have set up the framework to investigate the different choices for precise power estimation. This research has shown that a simpler timing model for circuit analysis, such as unit delay, can also provide high accuracy in early design stages. Furthermore, for many circuit designs, a simple linear regression shows accuracy comparable to more complex approaches under the assumption of limited structural information about the circuit. However, overall, the variance of accuracy was smaller for a more complex graph neural network. We presented these results at the ISQED conference and received the Best Paper Award for this work.

Solving the puzzle of transferable power dissipation modeling

Based on these results, we have identified further research questions. The GNN results also show that transferability (i.e., one model for different circuits) can be achievable for black-box circuits. This results in the need for a large number of diverse circuit designs. For research purposes, the number of available circuits is limited. Here, the automatic generation of artificial circuit designs is suitable. We have developed a concept to generate circuit designs with diverse power dissipation behavior to enable the development of transferable ML-based models. Furthermore, the designs must be simulated with diverse workloads to obtain sufficient switching activity data. The unit delay timing model has shown potential here but needs an efficient simulation tool. With bachelor's and master's degree students, we investigated the opportunities to develop a simple yet fast unit delay simulator using graph processing units. In addition, our project has shown that simple linear regression is helpful for power estimation in early design stages. Therefore, we are investigating hybrid models for simple yet transferable power estimation.

While the Rudolf Diesel Industry Fellowship of Sani Nassif at TUM-IAS is finished, the members of our Focus Group continue to work on these still open research questions to obtain highly accurate power estimation of digital ICs under limitations such as unknown circuit structure.

[1]

Zhang, Y., Ren, H. & Khailany, B. GRANNITE: Graph neural network inference for transferable power estimation. 2020 57th ACM/IEEE Design Automation Conference (DAC), 1–6 (2020).

[2]

Nasser, Y., Lorandel, J., Prévotet, J. C. & Hélard, M.. RTL to transistor level power modeling and estimation techniques for FPGA and ASIC: A survey. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems 40(3), 479–493 (2020).

[3]

Willard, J., Jia, X., Xu, S., Steinbach, M. & Kumar, V. Integrating physics-based modeling with machine learning: A survey. arXiv preprint arXiv:2003.04919 1(1), 1–34 (2020).

Selected publications

- Fengler, P., Nassif, S. & Schlichtmann, U. Toward Early Stage Dynamic Power Estimation: Exploring Alternative Machine Learning Methods and Simulation Schemes. 2024 25th International Symposium on Quality Electronic Design (ISQED), pp. 1–8 (2024).

- Fengler, P., Chen, J. Nassif, S. & Schlichtmann, U. Enabling Machine Learning for Power Modeling via Artificial Netlist Generation. Accepted by: 2025 IEEE International Symposium on Circuits and Systems (ISCAS).